# Fast Turn-Off Intelligent Controller With CC/CV Controller

#### DESCRIPTION

The MP6960 is a synchronous rectified controller for a high-efficiency flyback converter circuit. The controller has integrated voltage and current regulators for the secondary side of the converter, making it suitable for battery charging and as a secondary controller for switching regulator systems.

The MP6960 regulates the forward drop of an external switch to about 70mV and switches it off as soon as the voltage goes negative. It also has a light-load sleep mode to reduce the quiescent current to <300µA.

The MP6960 also compares the DC voltage and the current level at the output of a switching power supply to the voltage reference and current limitation, respectively. It provides feedback through an opto-coupler to the PWM controller IC at the primary side.

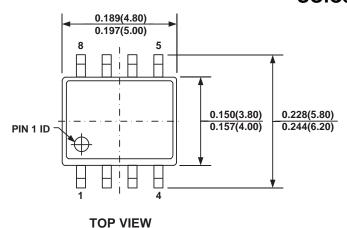

The MP6960 is available in an SOIC8 package.

#### **FEATURES**

- Works with 12V Standard and 5V Logic-Level FETS

- Compatible with Energy Star 1W Standby Requirements

- V<sub>DD</sub> to V<sub>SS</sub> Range from 8V to 24V

- V<sub>D</sub> to GND Range from 4.5V to 36V

- Fast Turn-Off Total Delay of 20ns

- Max. 400kHz Switching Frequency

- <400µA Quiescent Current in Light-Load Mode

- Supports CCM, DCM and Quasi-Resonant Topologies

- Supports High-Side and Low-Side Rectification

- Power Savings of up to 1.5W in a Typical Notebook Adapter

- 2.5V Built-In Voltage Reference with ±0.5% Accuracy

- 25mV Built-In Current Reference with ±5% Accuracy

- Constant Voltage and Constant Current Control

- Two Operational Amplifier with ORED Output and 1MHz Bandwidth

- 8-Pin SOIC8 Package

#### **APPLICATIONS**

- Industrial Power Systems

- Distributed Power Systems

- Battery Powered Systems

- Flyback Converters

All MPS parts are lead-free and adhere to the RoHS directive. For MPS green status, please visit MPS website under Products, Quality Assurance page. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

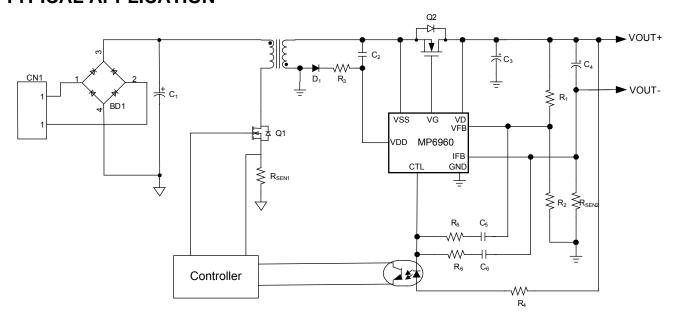

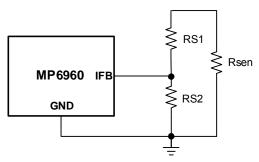

## **TYPICAL APPLICATION**

#### ORDERING INFORMATION

| Part Number | Package | Top Marking |

|-------------|---------|-------------|

| MP6960GS*   | SOIC8   | MP6960      |

| MP6960CGS** | SOIC8   | MP6960      |

<sup>\*</sup> For Tape & Reel, add suffix –Z (e.g. MP6960GS–Z);

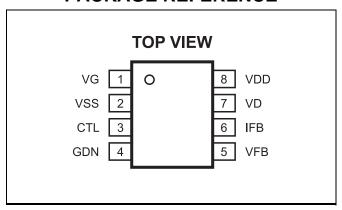

#### **PACKAGE REFERENCE**

### ABSOLUTE MAXIMUM RATINGS (1)

| V <sub>DD</sub> to V <sub>SS</sub> | 0.3V to +27V              |

|------------------------------------|---------------------------|

| GND to V <sub>SS</sub>             |                           |

| V <sub>G</sub> to V <sub>SS</sub>  | 0.3V to +27V              |

| V <sub>D</sub> to V <sub>SS</sub>  |                           |

| V <sub>D</sub> to GND              | 0.7V to +40V              |

| CTL to GND                         |                           |

| VFB, IFB to GND                    | 0.3V to +6.5V             |

| Maximum Operating Frequency        | 400 kHz                   |

| Continuous Power Dissipation       |                           |

|                                    | 1.4W                      |

| Junction Temperature               | 125°C                     |

| Lead Temperature (Solder)          | 260°C                     |

| Storage Temperature                |                           |

| Recommended Operating (            | Conditions <sup>(3)</sup> |

| V <sub>DD</sub> to V <sub>SS</sub> |                           |

|                                    |                           |

$V_D$  to GND......4.5V to 36V Maximum Junction Temp. (T<sub>J</sub>). -40°C to +125°C

# **Thermal Resistance** (4) **θ**<sub>JA</sub> **θ**<sub>JC</sub> SOIC8.......90 ......90 ..... 45... °C/W

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

<sup>\*\*</sup> For Tape & Reel, add suffix -Z (e.g. MP6960CGS-Z);

# **ELECTRICAL CHARACTERISTICS** (5)

$V_{DD} = 12V$ ,  $T_A = +25$ °C, unless otherwise noted.

| Parameter                                                                     | Symbol                           | Conditions                                                          | Min           | Тур  | Max  | Units |  |

|-------------------------------------------------------------------------------|----------------------------------|---------------------------------------------------------------------|---------------|------|------|-------|--|

| SYNCHRONOUS RECTIFIER O                                                       | SYNCHRONOUS RECTIFIER CONTROLLER |                                                                     |               |      |      |       |  |

| V <sub>DD</sub> Voltage Range                                                 |                                  | $V_{DD}$ - $V_{SS}$                                                 | 8             |      | 24   | V     |  |

| V <sub>DD</sub> UVLO Rising                                                   |                                  |                                                                     | 4.5           | 5.6  | 7    | V     |  |

| V <sub>DD</sub> UVLO Hysteresis                                               |                                  |                                                                     | 0.8           | 1    | 1.2  | V     |  |

| Operating Current                                                             | I <sub>cc</sub>                  | C <sub>LOAD</sub> =5nF, f <sub>SW</sub> =100kHz                     |               | 8    | 10   | mA    |  |

| Quiescent Current                                                             | I <sub>q</sub>                   | $V_{SS}$ - $V_D$ =0.5 $V$                                           |               | 2    | 3    | mA    |  |

| Shutdown Current of<br>Synchronous Rectifier<br>Controller                    | I <sub>shut_SR</sub>             | V <sub>DD</sub> =4V,V <sub>D</sub> =GND                             |               | 170  | 220  | μA    |  |

| Light-Load Mode Current                                                       |                                  |                                                                     |               | 260  | 360  | μΑ    |  |

| Thermal Shutdown                                                              |                                  |                                                                     |               | 150  |      | °C    |  |

| Thermal Shutdown Hysteresis                                                   |                                  |                                                                     |               | 30   |      | °C    |  |

| Turn-On Threshold (V <sub>SS</sub> -V <sub>D</sub> )                          | $V_{\text{fwd}}$                 |                                                                     | 55            | 70   | 85   | mV    |  |

| Turn on Dolov                                                                 | t <sub>Don</sub>                 | C <sub>LOAD</sub> = 5nF                                             |               | 150  |      | ns    |  |

| Turn-on Delay                                                                 | t <sub>Don</sub>                 | C <sub>LOAD</sub> = 10nF                                            |               | 250  |      | ns    |  |

| Input Bias Current on V <sub>D</sub> Pin                                      |                                  | V <sub>D</sub> = 180V                                               |               |      | 1    | μA    |  |

| Minimum On-Time (5)                                                           | t <sub>MIN</sub>                 | C <sub>LOAD</sub> = 5nF                                             |               | 1.6  |      | μs    |  |

| Light-Load–Enter Delay                                                        | t <sub>LL-Delay</sub>            | (R <sub>LL</sub> =100kΩ,integrated)                                 |               | 100  |      | μs    |  |

| Light-Load–Enter Pulse Width                                                  | t <sub>LL</sub>                  |                                                                     | 1.3           | 2    | 2.6  | μs    |  |

| Light-Load–Enter Pulse Width Hysteresis                                       | t <sub>LL-H</sub>                |                                                                     |               | 0.2  |      | μs    |  |

| Light-Load Mode Exit Pulse Width Threshold (V <sub>DS</sub> )                 | $V_{LL-DS}$                      |                                                                     | -400          | -250 | -150 | mV    |  |

| Light-Load Mode Enter Pulse Width Threshold (V <sub>GS</sub> ) <sup>(5)</sup> | $V_{LL\text{-GS}}$               |                                                                     |               | 1.0  |      | V     |  |

| GATE DRIVER SECTION                                                           |                                  |                                                                     |               |      | •    |       |  |

| V <sub>G</sub> (Low)                                                          |                                  | I <sub>LOAD</sub> =1mA                                              |               | 0.05 | 0.1  | V     |  |

| V (Lligh)                                                                     |                                  | V <sub>DD</sub> >17V                                                | 13            | 14   | 15   | V     |  |

| V <sub>G</sub> (High)                                                         |                                  | V <sub>DD</sub> <17V                                                | $V_{DD}$ -2.2 |      |      |       |  |

| Turn-off Threshold (V <sub>SS</sub> -V <sub>D</sub> )                         |                                  |                                                                     | 20            | 30   | 40   | mV    |  |

| Turn-off Propagation Delay                                                    |                                  | $V_D = V_{SS}$                                                      |               | 15   |      | ns    |  |

| Turn-Off Total Delay                                                          | t <sub>Doff</sub>                | $V_D = V_{SS}, C_{LOAD} = 5nF, R_{GATE} = 0\Omega$                  |               | 35   |      | ns    |  |

| Turn-On Total Belay                                                           | t <sub>Doff</sub>                | $V_D$ = $V_{SS}$ , $C_{LOAD}$ =10nF, $R_{GATE}$ =0 $\Omega$         |               | 45   |      | ns    |  |

| Pull-Down Impedance                                                           |                                  |                                                                     |               | 1    | 2    | Ω     |  |

| Pull-Down Current (5)                                                         |                                  | 3V <v<sub>G&lt;10V</v<sub>                                          |               | 2    |      | Α     |  |

| CC/CV CONTROLLER                                                              |                                  |                                                                     |               |      |      |       |  |

| Supply Current of CC/CV Controller                                            | I <sub>D</sub>                   | V <sub>D</sub> -GND = 15V, no load                                  |               | 90   |      | μΑ    |  |

| OPERATIONAL AMPLIFIER of CC/CV CONTROLLER                                     |                                  |                                                                     |               |      |      |       |  |

| Input Bias Current (5)                                                        | I <sub>B</sub>                   | T <sub>A</sub> = 25°C                                               | -50           | -10  | 0    | nA    |  |

| <del></del>                                                                   |                                  |                                                                     |               |      |      |       |  |

| Output Sink Current                                                           | I <sub>CTL_SINK</sub>            | $T_A = 25^{\circ}C, V_{CTL} = 0.5V$<br>-20°C = $T_A = +85^{\circ}C$ | 8             | 15   |      | mA    |  |

# ELECTRICAL CHARACTERISTICS (5) (continued)

$V_{DD} = 12V$ ,  $T_A = +25$ °C, unless otherwise noted.

| Parameter                       | Symbol                   | Conditions                                                                                                                                                                           | Min   | Тур | Max   | Units |  |

|---------------------------------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|-------|--|

| Supply Voltage Rejection Ratio  | SVR                      | Supply Voltage change of 1.0V                                                                                                                                                        | 65    | 90  |       | dB    |  |

| Common Mode Rejection Ratio (5) | CMRR                     |                                                                                                                                                                                      |       | 80  |       | dB    |  |

| Gain Bandwidth Product (5)      | GBW                      | $\begin{array}{lll} V_{D}\text{-}GND\text{=}15V, & V_{FB}(I_{FB})\text{-}\\ V_{REF}(I_{REF})\text{=}& 10\text{mV}, & R_{L} & \text{=}2k\Omega,\\ C_{L} = 100\text{pF} & \end{array}$ |       | 1   |       | MHz   |  |

| Output Leakage Current          | I <sub>CTL_LEAKAGE</sub> | T <sub>A</sub> = 25°C                                                                                                                                                                |       |     | 2     | μA    |  |

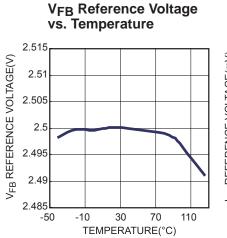

| VOLTAGE REFERENCE (MP6960)      |                          |                                                                                                                                                                                      |       |     |       |       |  |

| Reference Voltage               | $V_{REF}$                | I <sub>OUT</sub> = 1mA, T <sub>A</sub> = 25°C                                                                                                                                        | 2.475 | 2.5 | 2.525 | V     |  |

| Therefore voltage               |                          | 0°C . T <sub>A</sub> . 85°C <sup>(5)</sup>                                                                                                                                           | 2.47  | 2.5 | 2.53  | V     |  |

| VOLTAGE REFERENCE (MP6960C)     |                          |                                                                                                                                                                                      |       |     |       |       |  |

| Reference Voltage               | V <sub>REF</sub>         | I <sub>OUT</sub> = 1mA, T <sub>A</sub> = 25°C                                                                                                                                        | 2.488 | 2.5 | 2.512 | ٧     |  |

|                                 |                          | 0°C . T <sub>A</sub> . 85°C <sup>(5)</sup>                                                                                                                                           | 2.48  | 2.5 | 2.52  | V     |  |

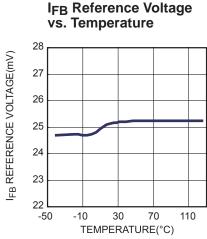

| CURRENT REFERENCE               |                          |                                                                                                                                                                                      |       |     |       |       |  |

| Reference Current               | V <sub>IREF</sub>        | I <sub>OUT</sub> =1mA, T <sub>A</sub> =25°C                                                                                                                                          | 24    | 25  | 26    | mV    |  |

| Treference Current              |                          | T <sub>A</sub> =0°C to 85°C <sup>(5)</sup>                                                                                                                                           | 23.75 | 25  | 26.25 | mV    |  |

#### Notes:

<sup>5)</sup> Guaranteed by Design and Characterization.

### TYPICAL PERFORMANCE CHARACTERISTICS

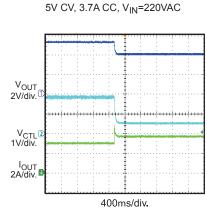

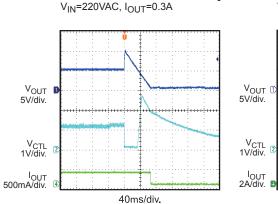

**CV Mode to CC Mode**

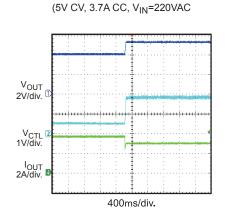

**CC Mode to CV Mode**

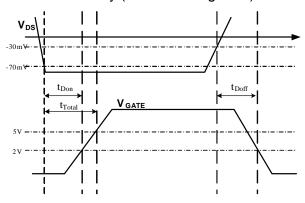

**OVP Function in 15W Flyback**

**OVP Function in 15W Flyback**

## **PIN FUNCTIONS**

| Pin# | Name | Description                                                                                                               |

|------|------|---------------------------------------------------------------------------------------------------------------------------|

| 1    | VG   | Gate Drive Output                                                                                                         |

| 2    | VSS  | Reference for VD. Connect to MOSFET source pin.                                                                           |

| 3    | CTL  | Output Common. Reference for voltage regulation and current limitation loops. Drives the primary side of an opto-coupler. |

| 4    | GND  | CC/CV controller ground.                                                                                                  |

| 5    | VFB  | Voltage Feedback. An external resistor divider from the output to GND tapped to the FB pin sets the output voltage.       |

| 6    | IFB  | Current Feedback. Connected to the sense resistor.                                                                        |

| 7    | VD   | MOSFET Drain Voltage Sense. Also the supply voltage of the CC/CV controller                                               |

| 8    | VDD  | Supply Voltage of the Synchronous Rectifier Controller                                                                    |

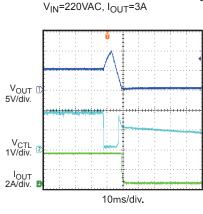

## **BLOCK DIAGRAM**

Figure 1: Functional Block Diagram

#### **OPERATION**

The MP6960 is a synchronous rectified controller for use in constant-current mode (CCM), discontinuous-current mode (DCM), and quasi-resonant topologies. MP6960 integrates a high-precision bandgap voltage reference, and two opamps to regulate and control the output voltage and current of the power supply.

#### **Blanking**

The control circuitry contains a blanking function that ensures that when the MOSFET turns on or off, it remains in that state for a minimal time period. The turn on blanking time is ~1.6µs, which determines the minimum on-time. During the turn-on blanking period, the turn-off threshold changes to approximately +50mV (instead of -30mV) to ensure that the part can always turn off even during the turn on blanking period (albeit slower, so do not set the synchronous period to less than 1.6µs in CCM for a flyback converter, or risk shoot through).

#### **Under-Voltage Lockout (UVLO)**

When the VDD drops below the UVLO threshold, the part enters sleep mode and the VG pin is pulled low by a  $10k\Omega$  resistor.

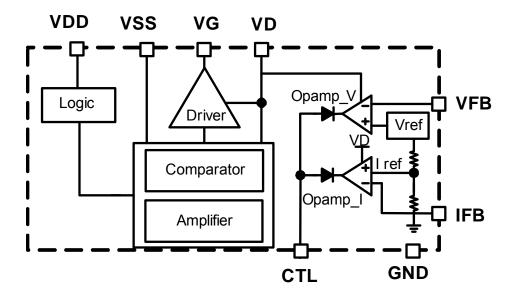

#### **Turn-On Phase**

When the synchronous MOSFET is ON, the current flowing through its body diode generates a negative  $V_{DS}$ . Because this body diode voltage drop (<-500mV) is much smaller than the turn-on threshold of the control circuitry (-70mV), then MP6960 will then pull the gate driver voltage high to turn on the synchronous MOSFET after a 150ns turn-on delay (Defined in Figure 2).

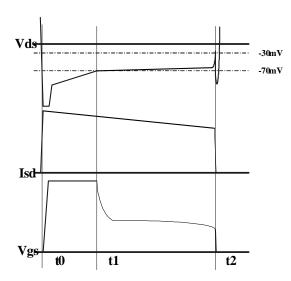

Figure 2: Turn-On and Turn-Off Delay

#### **Conducting Phase**

When the synchronous MOSFET turns ON,  $V_{DS}$  rises according to its ON resistance. As soon as  $V_{DS}$  rises above the turn-on threshold (-70mV), the control circuitry stops pulling up the gate driver, so the internal pull-down resistor ( $10k\Omega$ ) pulls down the gate voltage to increase the ON resistance of the synchronous MOSFET to slow the  $V_{DS}$  rise. This adjusts  $V_{DS}$  to around -70mV even when the current through the MOSFET is fairly small, and drop the driver voltage to fairly low levels when the synchronous MOSFET turns off to speed up turn-off (this driver-self-regulating function is still active during the turn-on blanking time so that the gate driver can turn off even with a very small duty).

#### **Turn-Off Phase**

When  $V_{DS}$  rises to trigger the turn-off threshold (-30mV), the control circuitry causes the gate voltage to go low after a 20ns turn-off delay (as shown in Figure 2) by the control circuitry. A 200ns blanking time—similar to the turn-on phase—after the synchronous MOSFET turns off avoids erroneous triggering.

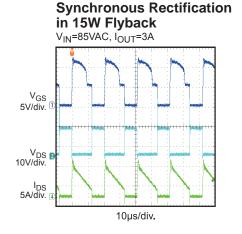

Figure 3 shows synchronous rectification at heavy loads. The gate driver initially saturates due to the high current. After  $V_{DS}$  rises above -70mV, gate driver voltage decreases to adjust  $V_{DS}$  to -70mV.

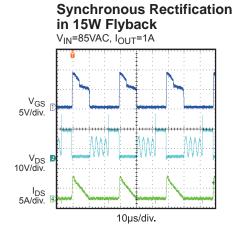

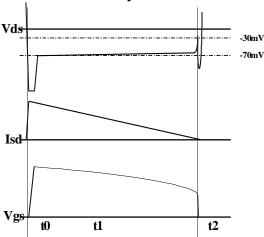

Figure 4 shows synchronous rectification under light loads. Due to the low current, the gate driver voltage never saturates but decreases as soon as the synchronous MOSFET turns on and adjusts  $V_{\rm DS}$ .

© 2012 MPS. All Rights Reserved.

Figure 3: Synchronous Rectification Operation at Heavy-Load

Figure 4: Synchronous Rectification Operation at Light-Load

#### **Light-Load Latch-Off Function**

The gate driver of the MP6960 latches to limit driver loss at light loads to improve efficiency. An internal resistor sets the light-load—enter pulse width,  $t_{LL}$ . When the synchronous MOSFET conducting period is less than  $t_{LL}$  for a longer than the light-load—enter delay  $(t_{LL-Delay})$ , the MP6960 enters light-load mode and latches off the gate driver. The synchronous MOSFET conducting period now starts when the gate driver turns on to when  $V_{GS}$  drops to the light-load—enter pulse width threshold  $(V_{LL-GS})$ .

During light-load mode, the MP6960 monitors the synchronous MOSFET body diode conducting

period by sensing  $V_{DS}$ . When  $V_{DS}$  exceeds the light-load—exit pulse width threshold— $V_{LL-DS}$ —the synchronous MOSFET body diode conducting period has ended. If the conducting period is longer than  $t_{LL}+t_{LL-H}$  ( $t_{LL-H}$ , light-load-enter pulse width hysteresis), the light-load mode has ended and the gate driver is unlatched to restart the synchronous rectification.

#### SR MOSFET Selection and Driver Ability

Selecting a power MOSFET requires trading off between  $R_{ON}$  and  $Q_G$ . For higher efficiency, chose a MOSFET with a smaller  $R_{ON}$ , though is typically  $Q_G$  is usually larger and slows turn-on/off speed and increases power loss. Because  $V_{DS}$  is regulated at -70mV during the driving period, avoid MOSFET with very small  $R_{ON}$  because a low gate driver level when the MOSFET current is still fairly high counters any efficiency gains from using a MOSFET with a low  $R_{ON}$ .

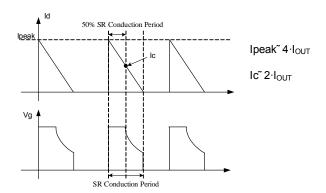

Figure 5 shows the typical waveform of QR flyback. Assume a 50% duty cycle and the output current is  $I_{\rm OUT}$ .

To make use of the MOSFET's low  $R_{\text{ON}}$ , the MOSFET be fully on for at least 50% of the SR conduction period:

$$V_{ds} = -I_{c} \times R_{on} = -2 \cdot I_{OUT} \times R_{on} \le -V_{fwd}$$

Where  $V_{DS}$  is the MOSFET drain-source voltage and  $V_{fwd}$  is the forward voltage threshold of the MP6960, which is ~70mV.

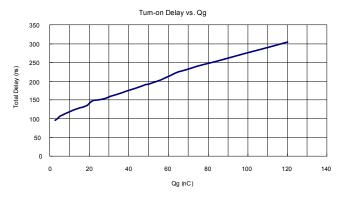

Based on these requirements, select a MOSFET with an  $R_{ON}$  no less than  $35/I_{OUT}$  (m $\Omega$ ). For example, for a 5A application, select  $R_{ON}$  no less than  $7m\Omega$ . Figure 6 shows the corresponding total delay during the turn-on period with different  $Q_G$  values. Driving a 120nC  $Q_G$  MOSFET, the MP6960 can pull up the MOSFET gate driver voltage to 5V in 300ns as soon as the body diode can conduct, which reduces turn-on power loss.

Figure 5: Synchronous Rectification of Typical Waveforms in QR Flyback

Figure 6: Total Turn-on Delay vs. QG

#### **Voltage Regulation Loop**

The voltage regulation is done by comparing the feedback output voltage (resistor divider R1 and R2) to the voltage reference (2.5V). If the feedback voltage exceeds 2.5V, the output of the voltage loop operational amplifier decreases. The opto-coupler current increases and reduces the output voltage by the way of the PWM controller.

#### **Current-Limit Loop**

Current limitation uses the voltage drop across the sense resistor,  $R_{\text{SEN}}$ , to measure the output current and compare it against the 25mV current reference. When the voltage across  $R_{\text{SEN}}$  exceeds 25mV, the output of the current loop operational amplifier decreases. The optocoupler current increases and reduces the output voltage by the way of the PWM controller.

# APPLICATION INFORMATION COMPONENT SELECTION

#### **Setting the Output Voltage**

Select the resistive voltage divider ratio to set the output voltage. The voltage divider drops the output voltage to 2.5V—the internal voltage reference. For most applications, use a  $10 k\Omega$  low-side resistor for the voltage divider. Determine the high-side resistor using the equation:

$$R1 = R2 \times (\frac{V_{OUT}}{2.5V} - 1)$$

Where R1 is the high-side resistor, R2 is the low-side resistor and  $V_{\text{OUT}}$  is the output voltage.

#### **Setting the Output Current**

$R_{\text{SEN}}$  is the sense resistor used for current measurement.

The current regulation is most effective when the voltage drop across R<sub>SEN</sub> equals the voltage of the current reference, 25mV.

$R_{\text{SEN}}$  can be realized with standard low cost 0.5W resistors in parallel.

$$I_{\text{OUT}} = \frac{V_{\text{REF}}}{R_{\text{SFN}}}$$

Where  $I_{\text{OUT}}$  is the output current, and  $V_{\text{REF}}$ =25mV.

In case the voltage drop across  $R_{\text{SEN}}$  always exceeds the voltage of the current reference (25mV),CTL will send a signal to the PWM controller to shutdown the PWM driver so that  $V_{\text{IFB}}$  remains around  $V_{\text{IREF}}$ . Figure 7 shows typical application in this case.

Figure 7: Typical IFB Application

$$I_{\text{OUT}} = \frac{V_{\text{REF}}}{R_{\text{SEN}}} \times \frac{Rs1 + Rs2}{Rs2}$$

Where RS1 is the high-side resistor, RS2 is the low-side resistor and  $I_{\text{OUT}}$  is the output current,  $V_{\text{REF}}$ =25mV.

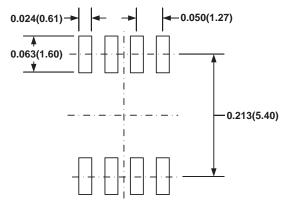

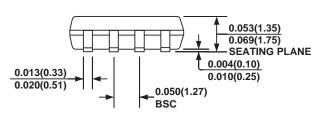

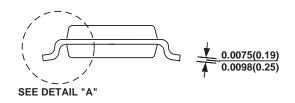

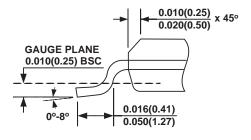

#### PACKAGE INFORMATION

### SOIC8

**RECOMMENDED LAND PATTERN**

**FRONT VIEW**

SIDE VIEW

**DETAIL "A"**

#### **NOTE:**

- 1) CONTROL DIMENSION IS IN INCHES. DIMENSION IN BRACKET IS IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS OR GATE BURRS.

- 3) PACKAGE WIDTH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSIONS.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.004" INCHES MAX.

- 5) DRAWING CONFORMS TO JEDEC MS-012, VARIATION AA.

- 6) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.